In the realm of wireless communication, autonomous vehicles, surveillance systems, and beyond, the performance of phase locked loops (PLLs) plays a crucial role. These components are responsible for the synthesis, modulation, and synchronization of oscillating signals, making them essential for high-speed and error-free operation of various technologies. However, in the case of fractional-N PLLs, a common type with excellent resolution and flexible frequency control, issues such as jitter and fractional spurs can significantly impact the overall performance of systems.

To address the challenges posed by fractional spurs in PLLs, a research team from Tokyo Institute of Technology (Tokyo Tech) led by Professor Kenichi Okada has developed two groundbreaking design techniques. The first method involves the implementation of a cascaded-fractional divider, which effectively splits the frequency control word (FCW) into two values that are far from an integer. This strategic approach helps filter out fractional spurs at higher frequencies within the PLL without the need for digital pre-distortion (DPD), which can introduce complexity and slow down the phase locking process.

The second innovative technique proposed by the Tokyo Tech researchers focuses on the use of a pseudo-differential digital-to-time converter (DTC) to address the limitations of conventional DTC designs. By leveraging the even-symmetric components present in the non-linearities of DTCs, the team implemented a dual half-range DTC operation that naturally cancels out the integral non-linearities (INLs) at the PLL’s phase detector. This approach not only minimizes fractional spurs but also optimizes power, delay range, noise, and overall performance of the PLL.

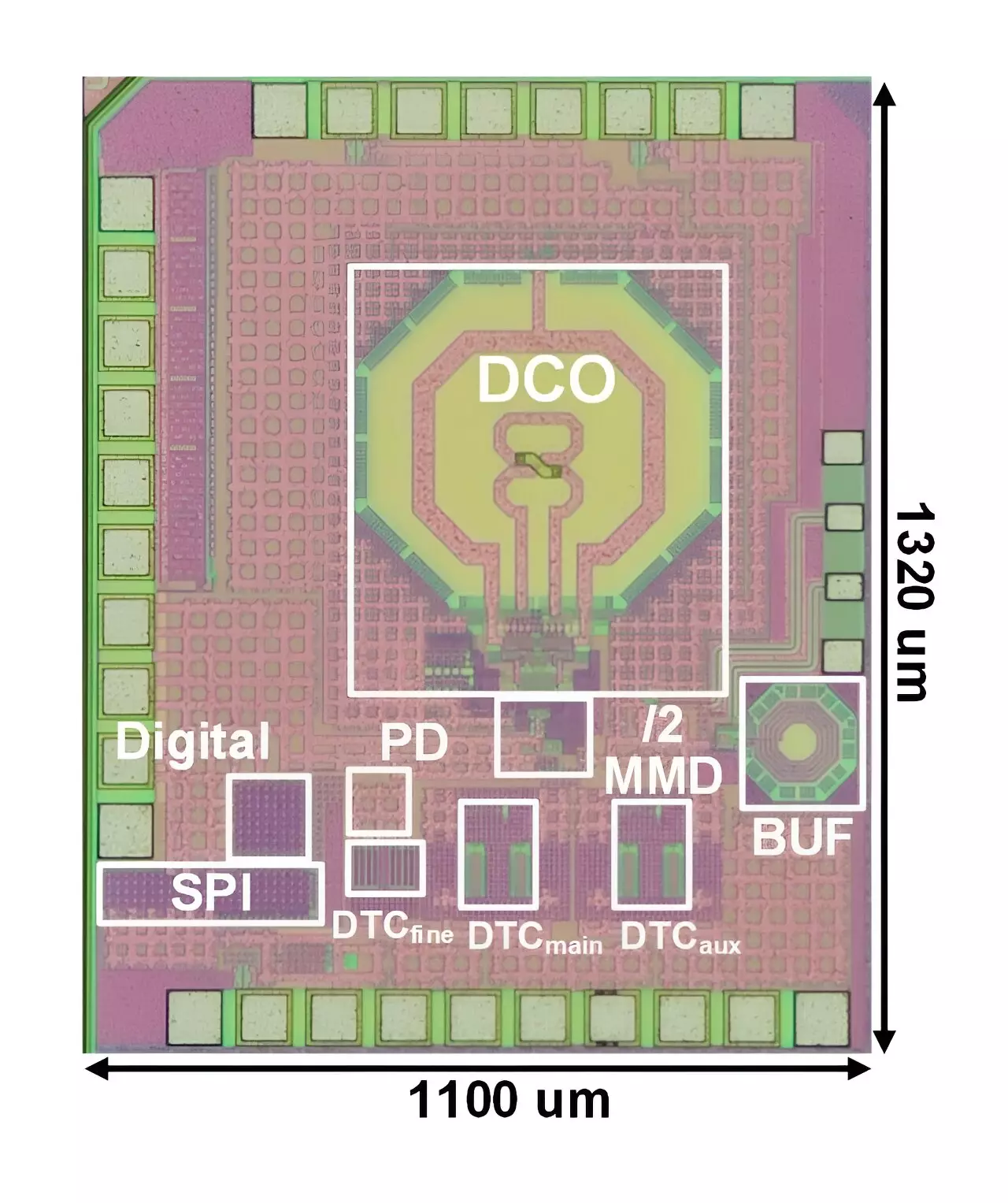

Through their experimental implementation of the low-spur fractional-N PLL using a 65 nm CMOS process, the Tokyo Tech researchers were able to achieve remarkable results. The active circuit area required for this innovative design was only 0.23 mm2, showcasing efficiency and compactness. In comparison to state-of-the-art designs, the performance improvements were evident, with a significant reduction in integrated PLL jitter from 243.5 fs to 143.7 fs. The combination of the cascaded-fractional divider and pseudo-differential DTC techniques led to the lowest class of jitter without the need for DPD technology, paving the way for enhanced performance in a wide range of applications relying on fractional-N PLLs.

The innovative design strategies introduced by the Tokyo Tech research team have the potential to revolutionize various industries and applications that utilize fractional-N PLLs. From advancing wireless communication technologies to enhancing the capabilities of autonomous vehicles, target tracking systems, and beyond, the low-spur PLL design offers a promising solution to mitigate the impact of fractional spurs and elevate the overall performance of critical systems. With ongoing developments in PLL technology, the future looks bright for a new era of enhanced wireless communication and beyond.

Leave a Reply